新闻中心

product center新闻中心

-

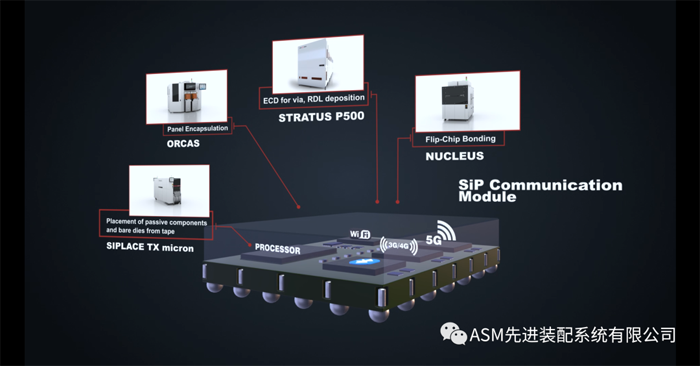

白皮书 | ASM针对SiP系统级封装的解决方案(中)

发布于:2022-03-23 09:44:31

上一篇我们讨论了SIPLACE在SiP应用中的高速及高精度能力,本篇我们来讨论SIPLACE如何应对极小元件以及裸芯片的贴装。

小元件贴装能力

SiP应用对于小元件的贴装能力要求是所有的SMT工艺中最高的。在英制01005大量使用的基础上,公制0201已经开始逐步导入。SIPLACE TX micron搭载的CP20M3贴装头不仅标配公制0201的贴装能力,并且可以全速贴装。背后的支撑除了高精度,还有一整套独到的贴装工艺。SIPLACE的X智能供料器基于其全闭环的精确控制,为小元件的贴装提供了供料保障。值得一提的是,任何标准的SIPLACE 8mm X供料器均有供应01005的能力。

而随着公制0201的逐步引入以及01005的包装趋势,4mm宽的供料器需求正在逐步增加。继承了SIPLACE X智能供料器的所有优点,SIPLACE 4mm X 供料器业已经过大量验证,即使料带只有4mm宽度,也可以接料以及通过接料传感器进行接料管控及精确追溯等。

裸芯片贴装能力

裸芯片的贴装是SiP区别于传统SMT的最主要制程之一。是否具备裸芯片的高速高质量贴装能力是机台是否具备SiP生产能力的重要标志。

SIPLACE TX micron具有完备的裸芯片贴装能力,分别体现在:

(1)供/取料

真空供料器可以确保连续供料时的裸芯片在料袋里的稳定性。

非接触式取料可以最大程度减少取料时对易碎裸芯片的压力施加。

取料前可以通过光学检查,过滤已经破裂的裸芯片。

(2)识别/处理

倒装芯片被普遍采用在SiP的应用中,而随着铜柱工艺的使用越来越趋势化,对传统元件影像识别能力带来了不小的挑战。基于铜柱工艺可以制作非常小的凸块,理论上直径可以小至25微米,这需要非常高解析度的元件相机。而传统的红光元件相机,往往也不能很好的区别铜柱上的镀锡层及其背景。

CP20M3贴装头配备的数字蓝光相机,可以很好的形成铜柱及背景的对比度,其可识别的最小凸块直径可以小至25微米,最小凸块步距可以小至50微米。

而该元件相机的功能不仅仅局限于元件中心的确定,对于元件本身的质量也可以进行把关。除了对SMD元件的各种不良,诸如翻面,侧立,氧化,缺球等有着高质量的识别率之外,也可以识别出裸芯片的崩裂。

Dipping是SiP常用的工艺之一。SIPLACE LDU 2X可以提供厚度非常精确的助焊剂层以供蘸取。对于NPI阶段的助焊剂厚度设置,可以通过在一个Cavity里设置多层厚度甚至自动厚度调整来实现。

在实际量产中,为了避免助焊剂余量不足以及减少人为的干预,可以自动进行助焊剂添加。

而对于助焊剂蘸取的质量,元件相机也可以进行判断,哪怕是透明的助焊剂,也可以识别出来。

(3)贴装

区别于传统的SMD贴装,裸芯片的贴装对于贴装压力的要求极高。TX micron搭载的CP20M3贴装头可以实现程序可控的精准压力贴装,并基于此衍生出业内独到的贴装高度自适应功能。

随着第二代甚至第三代半导体材料的大量使用,裸芯片的易碎性要求贴装设备具有更小更精确的贴装压力。CP20M3可以提供程序可控的低至0.5N的贴装压力。

而对于非常薄的裸芯片,CP20M3甚至可以提供接近于0N的“非接触式”贴装。

而对于贴装过程中可能产生的异常,如异常翘曲导致的贴装高度的突然大幅变化,TX micron会触发自适应的动作,如使用PCB相机检测贴装后的元件,自动调整贴装曲线等。

未完待续